L2S Talk by Moritz Nottebaum (University of Udine): Beyond MACs – Hardware-Aware Neural Network Design for Efficient Inference

30 October 2025, 10.00 h in H-A 7114

The talk is part of the ZESS lecture series and hosted by the DFG research unit “Learning to Sense” (L2S).

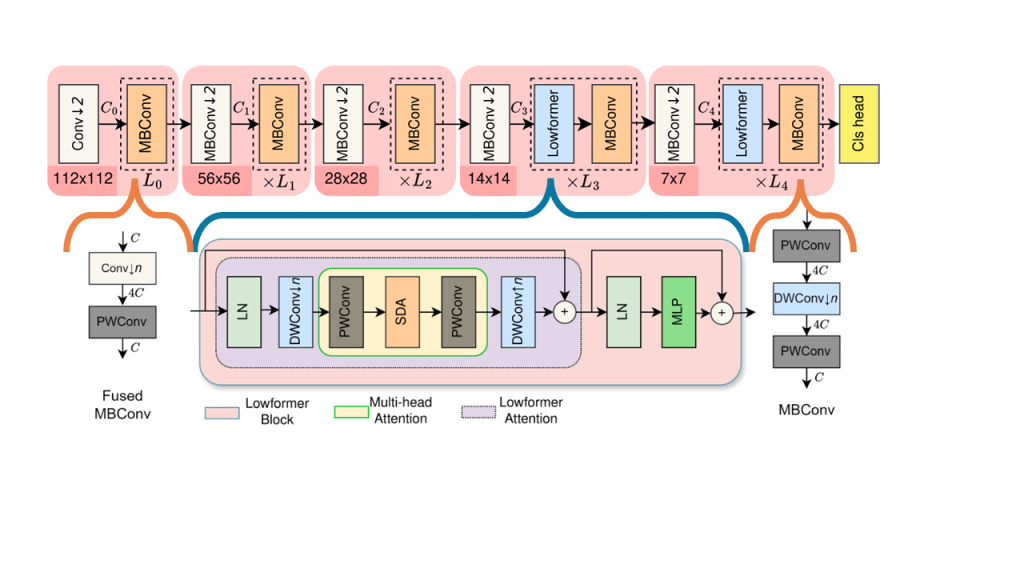

In this talk, Moritz will present his previous and current research, which mainly focuses on hardware-efficient neural network design. Traditionally, the execution efficiency of deep learning models has been estimated by counting the number of operations required for inference (MACs or FLOPs). However, the number of MACs or FLOPs can be poorly correlated with a model’s actual execution time, depending on the model architecture and hardware characteristics. This is largely due to two factors that considerably influence execution time: the degree of parallelism and memory access cost.

Moreover, optimizing models solely by minimizing MAC counts has reached a plateau in many domains, while the broader topic of hardware-aware design remains largely underexplored. By examining how architectural choices affect hardware efficient execution, we can derive design principles that unlock new levels of efficiency – opening an exciting and still emerging research area.

Finally, Moritz will discuss ongoing work, including efficient designs for visual object tracking and object detection, as well as a systematic framework for evaluating and comparing speed–accuracy trade-offs.

Moritz Nottebaum is a PhD student at the University of Udine.